#ahb dma ip verilog

Explore tagged Tumblr posts

Text

The AXI DMA Controller IP is a digital block used in FPGA designs to transfer data between memory and AXI-compatible peripherals without CPU intervention, enabling high-speed, efficient data movement using Direct Memory Access (DMA).

#ahb dma controller#axi dma ip core#axi dma scatter gather#ahb dma verilog#axi dma verilog#axi dma controller ip#axi bridge ip core#ahb dma ip verilog#axi stream dma#axi4 stream dma#axi4 data mover

0 notes

Link

0 notes

Photo

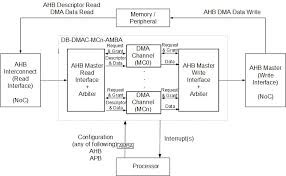

Ahb Dma Controller for CPU Programming--

Digital Blocks DMA Controller IP Cores offer a flexible CPU programming interface and high-performance transfer rates with leading AMBA Interconnects and standard or customized peripheral interfaces. Digital Blocks DMA Controllers are feature-rich with Multi-Channel, Scatter-Gather capability with IP releases targeting CPU AXI/AHB backbone DMA Engines, PCI Express DMA, or Peripheral high/low data-rate DMA transfers. More can be viewed @ https://www.digitalblocks.com/dma.html

0 notes

Text

Innovations in AHB DMA Controller for High-Speed Memory Access

In the rapidly evolving field of digital technology, efficient memory access remains a critical factor for system performance. At the heart of this challenge lies the AHB DMA controller, a key component designed to manage direct memory access with precision and speed. Digital Blocks has been at the forefront of innovating this technology, refining the AHB DMA controller to meet the demanding needs of modern applications.

Understanding the Role of the AHB DMA Controller

The AHB DMA controller plays a pivotal role in facilitating high-speed data transfers between memory and peripherals without burdening the central processing unit. By enabling direct memory access, this controller significantly reduces latency and frees up processing power for other critical tasks.

Digital Blocks has recognised the importance of this function and invested in enhancing the efficiency and reliability of the AHB DMA controller. These innovations allow for smoother data flow and improved system responsiveness, which are essential for industries relying on high-performance computing.

Enhancements in Data Transfer Efficiency

One of the significant advancements introduced by Digital Blocks in the AHB DMA controller involves optimising data transfer protocols. By improving how the controller manages burst transfers and prioritises data requests, the new designs achieve faster throughput rates.

This optimisation ensures that large blocks of data move seamlessly between system components, reducing bottlenecks that traditionally slow down operations. The result is a system that performs consistently at high speeds, meeting the rigorous standards of applications such as multimedia processing, communication devices, and embedded systems.

Robustness and Flexibility in Design

Digital Blocks’ approach to the AHB DMA controller also emphasises robustness and adaptability. The controller now supports multiple channel operations, allowing simultaneous data transfers without conflict. This multi-channel capability is crucial for systems that require parallel processing and multitasking.

In addition, the controller design offers configurability to match specific application requirements. This flexibility means that engineers can tailor the AHB DMA controller to optimise performance according to system needs. Such customisation ensures better power management and resource allocation, contributing to overall system efficiency.

Integration with Advanced System Architectures

The continuous development of the AHB DMA controller by Digital Blocks aligns well with the trends in system architecture. Modern designs increasingly demand controllers that integrate seamlessly with advanced bus systems and processors.

By maintaining compliance with industry standards and supporting a wide range of protocols, the AHB DMA controller fits into diverse system environments. This compatibility simplifies integration, reduces development time, and lowers costs. It also ensures that the controller remains relevant as new technologies emerge.

Conclusion: Leading the Future of Memory Access

The innovations introduced by Digital Blocks in the AHB DMA controller mark a significant step forward in high-speed memory access. By focusing on efficiency, robustness, and integration, these developments provide a reliable solution for today’s demanding digital systems.

As technology continues to advance, the need for powerful memory management tools will only grow. Digital Blocks’ commitment to refining the AHB DMA controller ensures that it remains a key player in supporting the future of high-performance computing.visit our website

#ahb dma controller#axi dma ip core#ahb dma verilog#axi4 stream dma#axi dma controller ip#axi dma scatter gather#axi bridge ip core#axi dma verilog#axi stream dma#axi4 data mover

0 notes

Text

#ahb dma controller#axi dma ip core#axi dma scatter gather#axi bridge ip core#axi dma verilog#axi dma controller ip#axi stream dma#ahb dma verilog#axi4 stream dma#axi4 data mover

0 notes

Text

#ahb dma controller#axi dma scatter gather#axi dma ip core#axi bridge ip core#axi dma verilog#ahb dma verilog#axi dma controller ip#axi4 data mover#axi stream dma#axi4 stream dma

0 notes

Text

Reducing Latency in Real-Time Applications with AXI4 Stream DMA

In real-time systems, every microsecond counts. Industries like telecommunications, automotive, medical, and defense demand instant data movement between processing units. Any delay can affect performance, accuracy, or safety. Digital Blocks, through its advanced design of AXI4 Stream DMA, is addressing this demand with precision and efficiency.

The Need for High-Speed Data Transfer

Real-time applications depend on the continuous and rapid flow of data. Tasks such as video processing, sensor fusion, and control systems require minimal delay between data capture and action. Standard memory-mapped data transfers often introduce latency due to handshaking, memory access, and software intervention. This slows down systems that must respond without delay.

The AXI4 Stream DMA developed by Digital Blocks helps bypass these barriers. It supports direct data transfers between sources and destinations with minimal CPU involvement. This makes it ideal for applications that require predictable and fast performance.

How AXI4 Stream DMA Improves System Speed

The AXI4 Stream DMA core is built to handle large volumes of data at high speed. It supports streaming data interfaces, where information is transferred in a continuous flow. This design reduces the overhead of individual memory transactions and avoids congestion that slows down traditional DMA systems.

By handling data transfers autonomously, the AXI4 Stream DMA allows the processor to focus on higher-level tasks. Digital Blocks has designed this module to be both lightweight and powerful, ensuring it fits into a wide range of system-on-chip (SoC) designs without consuming unnecessary resources.

Scalability for Complex Applications

Real-time systems vary in size and function. Some may require small and frequent data packets, while others need high-bandwidth continuous streaming. Digital Blocks addresses this need through a scalable AXI4 Stream DMA solution. It supports configurable parameters to match system architecture and data flow requirements.

Developers working on multi-core designs or FPGA-based systems can integrate AXI4 Stream DMA to improve performance while keeping latency under control. The design supports burst transfers, flow control, and error detection, all key features that enhance reliability.

Proven in Real-World Applications

Digital Blocks has delivered its AXI4 Stream DMA core to customers across multiple sectors. In each case, the goal was clear: reduce latency and improve data throughput without compromising system stability. Applications such as real-time video encoding, radar signal processing, and industrial automation have shown marked improvements after adopting this design.

By focusing on a robust, standards-based solution, Digital Blocks ensures that the AXI4 Stream DMA integrates smoothly with existing AXI-based systems. This reduces the time and cost of development while improving end-product performance.

Building the Future of Low-Latency Systems

Latency will always be a concern in real-time systems. However, the right architecture can bring it within acceptable limits. The AXI4 Stream DMA by Digital Blocks provides a focused solution to this challenge. With careful design and proven efficiency, it supports the fast, consistent data flow that modern systems demand.

As real-time applications continue to grow in complexity, Digital Blocks remains committed to delivering high-performance solutions that keep pace with future needs. More details visit us

#ahb dma controller#axi4 stream dma#axi bridge ip core#axi dma controller ip#ahb dma verilog#axi dma scatter gather#axi dma ip core#axi dma verilog#axi4 data mover#axi stream dma

0 notes

Text

#ahb dma controller#axi dma scatter gather#ahb dma verilog#axi dma ip core#axi dma controller ip#axi dma verilog#axi stream dma#axi bridge ip core#axi4 stream dma#axi4 data mover

0 notes

Text

AXI DMA Scatter Gather Enhancing Real-Time Data Streaming in SoC Designs

In today’s high-performance SoC designs, real-time data movement plays a critical role. Applications in communications, video processing, and AI demand reliable and efficient data streaming. To support these demands, AXI DMA Scatter Gather has become a powerful tool. At the forefront of this advancement stands Digital Blocks, delivering IP solutions that streamline data flow with precision and speed.

Meeting High-Speed Data Requirements

System-on-Chip designs today face increasing pressure to handle complex workloads with minimal latency. Traditional DMA approaches often fall short in scenarios where data sources and destinations are fragmented. AXI DMA Scatter Gather addresses this problem by allowing data transfers across non-contiguous memory regions without software intervention for each block.

Digital Blocks provides AXI DMA Scatter Gather IP that ensures consistent data flow in real-time systems. This approach helps manage bandwidth and reduces CPU load, which is critical in time-sensitive applications. With fewer interrupts and lower processing overhead, system responsiveness improves across all operations.

Smart Buffer Management

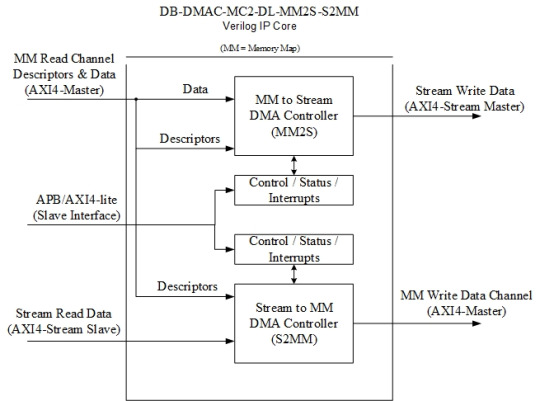

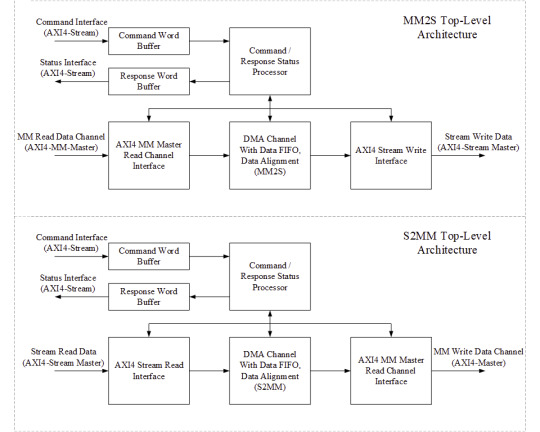

The AXI DMA Scatter Gather model enables intelligent buffer management. It uses a descriptor-based mechanism to define memory segments. Each descriptor holds address, length, and control data for a segment. The DMA engine reads these descriptors and processes them autonomously.

Digital Blocks integrates this structure with a focus on flexibility and stability. Their IP handles both memory-to-stream and stream-to-memory directions efficiently. It supports continuous and burst transfers with minimal CPU involvement. This results in streamlined operations that are ideal for multi-channel or multi-core systems.

Supporting Advanced Use Cases

Applications like 4K video processing, machine learning, and software-defined radio benefit directly from AXI DMA Scatter Gather. These use cases require large amounts of data to be moved quickly and reliably. Any delay can disrupt system behavior or cause quality issues.

Digital Blocks designs their AXI DMA Scatter Gather IP to match such requirements. It supports programmable burst sizes, interrupt coalescing, and address alignment. This ensures that the IP adapts to system needs without placing stress on core resources. In environments where data integrity and speed matter, this feature set makes a measurable difference.

Seamless SoC Integration

Another strength of Digital Blocks' solution lies in its ease of integration. The AXI interface enables smooth connection with standard bus architectures used in SoC designs. The IP core works with AXI4 and AXI4-Stream protocols, allowing wide compatibility across platforms.

Digital Blocks supports engineers through every phase of implementation. Their design ensures scalability, making it suitable for both low-power embedded designs and high-throughput computing systems. It helps reduce development time and allows design teams to focus on application-level innovation.

Driving Innovation in Real-Time Systems

AXI DMA Scatter Gather by Digital Blocks is helping shape the future of real-time data streaming in SoCs. Its efficient use of system memory, reduced CPU intervention, and high-speed performance make it a valuable asset in advanced designs.

By focusing on reliability and intelligent data handling, Digital Blocks continues to deliver IP that meets today’s performance challenges and prepares systems for tomorrow’s demands. For more details visit us

#ahb dma controller#axi dma ip core#axi dma controller ip#axi stream dma#axi bridge ip core#ahb dma verilog#axi dma scatter gather#axi4 data mover#axi dma verilog#axi4 stream dma

0 notes

Text

axi4 stream dma

Elevate your system's data handling capabilities with our cutting-edge Digital Blocks AXI4 Stream DMA controller. Engineered for efficiency and speed, this module facilitates seamless data transfers between various peripherals and memory units. Incorporating the latest AXI4 protocol standards, this DMA controller ensures smooth and reliable data transmission for various applications. Visit Us https://www.digitalblocks.com/dma-verilog-ip-cores/

0 notes

Text

AXI DMA IP Core: Optimizing High-Performance Data Transfers in FPGA Systems

In FPGA (Field-Programmable Gate Array) systems, efficient data transfer is crucial for optimal performance. The AXI DMA IP Core (Advanced eXtensible Interface Direct Memory Access Intellectual Property Core) plays a vital role in facilitating high-speed data movement between memory and peripherals, minimizing CPU involvement and enhancing overall system efficiency.

Understanding AXI DMA IP Core

The AXI DMA IP Core is designed to handle direct memory access operations within FPGA architectures. It enables peripherals to directly read from or write to memory without continuous CPU intervention, thereby reducing latency and freeing up processor resources for other tasks.

Key Features of AXI DMA IP Core

High Throughput: Supports data widths ranging from 32 to 1024 bits, allowing for rapid data transfers suitable for both small and large datasets.

Scatter-Gather Capability: Utilizes scatter-gather lists to manage data transfers efficiently, supporting various transfer scenarios such as memory-to-memory, peripheral-to-memory, and peripheral-to-peripheral.

Flexible Configuration: Offers a configurable number of channels (from 1 to 16), each with independent read and write controllers, enabling tailored solutions for specific application requirements.

Compliance with AMBA Standards: Fully compliant with AMBA AXI4 and AXI3 interconnects, ensuring seamless integration into existing FPGA designs.

Digital Blocks' AXI DMA IP Core Solutions

At Digital Blocks, we specialize in providing high-quality AXI DMA IP Core solutions tailored to meet the diverse needs of FPGA system designers. Our offerings include:

Multi-Channel Support: Our AXI DMA Controllers support 1 to 16 independent data transfer channels, each with scatter-gather capabilities, ensuring efficient data movement across various system components.

High-Performance Design: Optimized for both small and large data sets, our DMA controllers excel in delivering high data throughput, crucial for applications requiring rapid data processing.

Comprehensive Integration: Fully compliant with AMBA AXI4 and AXI3 interconnects, our IP cores integrate seamlessly into existing FPGA designs, facilitating smooth system development and deployment.

Customizable Features: We offer flexible configurations, allowing designers to tailor the DMA controller's features to specific application requirements, ensuring optimal performance and resource utilization.

Conclusion

Implementing an AXI DMA IP Core is essential for optimizing high-performance data transfers in FPGA systems. By offloading data movement tasks from the CPU, it enhances system efficiency, reduces latency, and improves overall performance. Digital Blocks is committed to providing robust and flexible AXI DMA IP Core solutions, empowering designers to achieve their performance goals in various FPGA applications. For More Details:- https://www.digitalblocks.com/?utm_source=SEO&utm_medium=SEO&utm_campaign=blog

0 notes

Text

AXI Stream DMA

Digital Blocks offers advanced AXI Stream DMA solutions, enabling high-speed data transfer between memory and peripherals in FPGA and ASIC designs. Our efficient AXI Stream DMA IP cores support low-latency, high-throughput applications in networking, video processing, and embedded systems. With customizable features, seamless integration, and optimized performance, Digital Blocks ensures reliable and scalable solutions for your design needs. Enhance your system’s efficiency with our industry-leading AXI Stream DMA solutions. Contact us today!

0 notes

Text

Digital Blocks offers high-performance AXI Bridge IP Core solutions, enabling seamless data transfer and protocol conversion for FPGA and ASIC designs. Our AXI bridges ensure efficient communication between AXI-based systems, supporting AXI-to-AHB, AXI-to-APB, and AXI-to-PCIe interfaces with low latency and high throughput. Designed for scalability and customization, our IP cores optimize embedded systems, high-performance computing, and SoC architectures. For More Details Visit Us.

#ahb dma controller#axi dma scatter gather#axi dma ip core#axi stream dma#axi4 stream dma#ahb dma verilog

0 notes

Text

Enhancing High-Speed Data Transfers with AXI DMA Scatter-Gather: A Complete Guide!

Efficient data movement is crucial in high-performance computing and embedded systems. AXI DMA Scatter-Gather plays a vital role in optimizing high-speed data transfers, reducing CPU workload, and enhancing overall system efficiency. In this guide, we will explore the fundamentals of AXI DMA Scatter-Gather, its advantages, and how Digital Blocks provides industry-leading solutions to meet your design needs.

Understanding AXI DMA Scatter-Gather

AXI DMA Scatter-Gather is an advanced Direct Memory Access (DMA) technique that enables efficient data transfer across multiple memory locations. Unlike traditional DMA, which moves data in fixed blocks, scatter-gather mode allows data to be transferred dynamically, improving system flexibility and performance.

Key Benefits of AXI DMA Scatter-Gather:

Reduced CPU Overhead: By offloading data movement tasks, it frees up CPU resources for other critical operations.

Increased Data Transfer Efficiency: It minimizes memory fragmentation and optimizes data throughput.

Low-Latency Performance: Ideal for real-time applications requiring high-speed data processing.

Scalability: Supports high-bandwidth applications in networking, video processing, and AI/ML systems.

How AXI DMA Scatter-Gather Works

The Scatter-Gather mechanism in AXI DMA utilizes a descriptor-based architecture, where each descriptor defines the source, destination, and transfer parameters. This enables seamless handling of multiple data chunks without CPU intervention.

The Process Includes:

Descriptor Preparation: The CPU prepares a linked list of descriptors for data movement.

DMA Controller Execution: The AXI DMA engine reads the descriptors and executes transfers autonomously.

Completion Notification: The system receives an interrupt when the transfer is complete, ensuring seamless data flow.

Digital Blocks: Leading the Way in AXI DMA Scatter-Gather Solutions

At Digital Blocks, we specialize in providing silicon-proven AXI DMA Scatter-Gather IP cores designed to enhance the performance of your FPGA, ASIC, and SoC designs. Our high-performance DMA controllers enable efficient, low-latency data movement, making them ideal for applications in networking, automotive, video processing, and artificial intelligence.

Why Choose Digital Blocks?

Proven Expertise: Over two decades of experience in developing high-speed IP cores.

Optimized Performance: Designed for high-throughput, low-latency applications.

Seamless Integration: Fully compatible with industry-standard AXI architectures.

Customizable Solutions: Tailored to meet specific project requirements.

Conclusion

AXI DMA Scatter-Gather is a game-changer in high-speed data transfers, enabling efficient memory management and reducing CPU workload. With Digital Blocks' industry-leading AXI DMA solutions, engineers can accelerate their designs, improve system performance, and achieve faster time-to-market. For More Details:- https://www.digitalblocks.com/axi-dma-verilog-ip-core/

0 notes

Text

AXI DMA Scatter-Gather is a powerful data transfer technique that enhances the performance of high-speed systems by efficiently managing memory buffers in an AXI-based architecture. By allowing direct memory access (DMA) between multiple locations, the Scatter-Gather method significantly reduces CPU load and accelerates data transfer operations. At Digital Blocks, we offer advanced AXI DMA Scatter-Gather IP cores, designed to seamlessly integrate into your system, providing optimized performance and low latency for high-throughput applications. For More Details Visit Us.

#axi dma scatter gather#axi dma ip core#axi dma verilog#axi dma controller ip#axi bridge ip core#ahb dma controller

1 note

·

View note